Intel will neue Chip-Architekturen künftig länger nutzen

Es gibt damit die als “Tick-Tock”-Strategie bezeichnete Vorgehensweise auf. So wurde der im Jahresrythmus abwechselnd vollzogene Schritt entweder zu einer neuen Architektur oder auf eine geringere Fertigungsbreite bezeichnet. Nun folgt darauf eine Optimierungsphase. Jährlich neue Produkte wird es auch weiterhin geben.

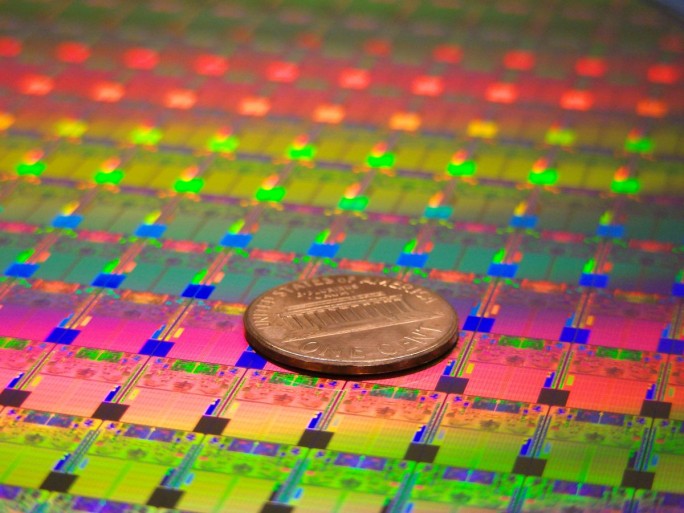

Intel hat sich nun offiziell von der vor einem Jahrzehnt eingeführtenm, als “Tick-Tock” bezeichneten Vorgehensweise bei Produktion und Vermarktung seiner Chips verabschiedet. “Tick-Tock” stand für den im Jahresrhythmus erfolgten Wechsel entweder auf eine neue Architektur oder eine geringere Fertigungsbreite (auch als Die-Shrink bezeichnet). Damit wurden Proudukte mit einer neuen Prozessorarchitektur immer mit einem bewährten Fertigungsprozess hergestellt (“Tick”) und konnte ein neuer Fertigungsprozess mit geringerer Strukturbreite immer mit einer bereits etablierten Architektur (“Tock”) begonnen werden.

In Zukunft soll “Tick-Tock” dann um einen dritten Schritt, die Optimierung, ergänzt werden. Das geht aus einer Pflichtmitteilung (PDF) an die US-Börsenaufsicht SEC hervor. In dem Bericht kündigt Intel eine längere Nutzung eines einmal eingeführten Fertigungsprozesses an. Es begründet das damit, dass die Umstellung auf ein neues Verfahren immer komplexer werde. Zudem dauere es auch länger, bis eine zufriedenstellende Produktionsausbeute erzielt werde.

Beides sind Indikatoren dafür, dass sich die Produktion dem physikalisch überhaupt noch machbaren nähert. Aus diesem Grund experimentieren zum Beispiel Firmen IBM und Hewlett Packard Enterprise bereits mit neuen Konzepten,. Bei IBM liegt der Schwerpunkt auf Quantencomputing, das aber obwohl bereits erhbeliche Hürden überwunden wurden, aber noch sehr in den Kinderschuhen steckt. Hewlett Packard Enterprise ist mit den sogennanten Memristoren, mit denen dann künftig auf einer anderen Basis deutlich mehr und anders geartete Rechenleistung in kompakter Form verfügbar werden soll, schon erheblich weiter. Zum Beispiel wurde auf der CeBIT ein erster, voll funktionsfähiger Memristor mit der etwa einer Streichholzschachtel entsprechenden Oberfläche gezeigt. Der ist HPE aber noch zu groß, nun gilt es, den Fertigungsprozess in Bezug auf die Miniaturiserung zu verfeinern. Bis es soweit ist, kann sich aber Intel offenbar erlauben, das Innovationstempo etwas zu drosseln.

In dem der SEC vorgelegten Dokument heißt es: “Wir erwarten durch weitere Optimierung unserer Produkte und Herstellungsverfahren eine Verlängerung des Zeitraums, in dem wir unsere 14-nm-Herstellungstechnik und unsere kommende 10-nm-Generation nutzen, während wir den jährlichen Rhythmus unserer Produkteinführungen einhalten.” Konkret bedeutet dass, dass mit “Kaby Lake” dann dieses Jahr der dritter Prozessor aus der 14-nm-Fertigung kommt, bevor 2017 die 10-nm-Fertigung aufgenommen wird.

Der Chiphersteller bezeichnet das neue Vorgehen als “Process-Architecture-Optimization” (PAO). Es zeichnete sich bereits in der Praxis ab: Bereits mit dem Haswell Refresh rund zehn Monate nach Vorstellung der ersten Haswell-Prozessoren, erfuhren viele Modelle nur eine leicht verbesserte Performance durch eine um 100 MHz angehobene Taktrate. Dieser Schritt würde nun nachträglich in die offizielle als “optimierung” bezeichnete Phase fallen.

Für Kaby Lake, dem drittem Produkt aus der 14-Nanometer-Fertigung, verspricht Intel nun aber dennoch “entscheidende Leistungsfortschritte verglichen mit der sechsten Generation der Core-Prozessoren”. Der erneuerte Prozessor soll im zweiten Halbjahr 2016 auf den Markt kommen. 2017 soll dann die 10-Nanometer-Fertigung beginnen.

[mit Material von Bernd Kling, ZDNet.de]

<!– Tipp: Wie gut kennen Sie sich mit Prozessoren aus? Testen Sie Ihr Wissen – mit 15 Fragen auf ITespresso –>Tipp: Wie gut kennen Sie sich mit Prozessoren aus? Überprüfen Sie Ihr Wissen – mit dem Quiz auf silicon.de.